Hexagonal Storage Scheme for Interleaved Frame Buffers and Textures

Yosuke Bando

Takahiro Saito

Masahiro Fujita

TOSHIBA Corporation

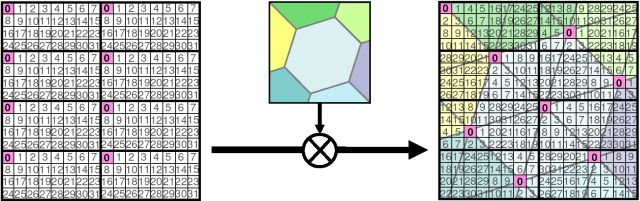

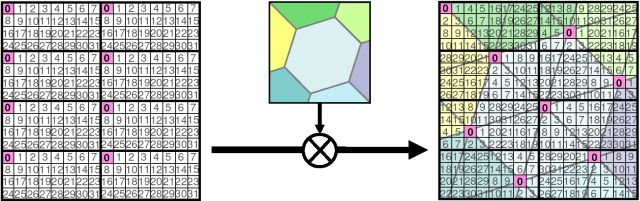

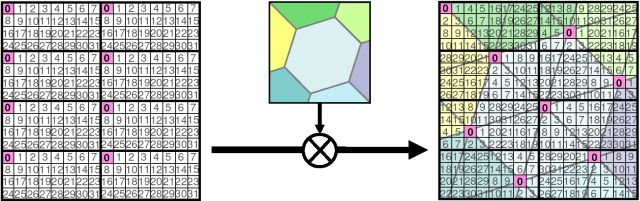

This paper presents a storage scheme

which statically assigns pixel/texel coordinates to multiple memory banks

in order to minimize frame buffer and texture memory access load imbalance.

In this scheme,

the pixels stored in a particular memory bank are placed

at the center and the vertices of hexagons packed in the frame buffer.

By making these hexagons close to regular

so that the pixel placement is uniform and isotropic,

frame buffer and texture memory accesses are evenly distributed over the memory banks.

The analysis of memory access patterns in rendering typical 3D graphics scenes

shows that the hexagonal storage scheme

can reduce rendering performance degradation due to bank conflicts

by an average of 10%

compared to the traditional rectangular storage scheme.

- Paper (2.2MB, PDF):

Proceedings of SIGGRAPH/Eurographics Workshop on Graphics Hardware 2005, pp. 33-40, 2005.

The presented storage scheme assigns pixel coordinates

to multiple (in this case 32) memory banks,

by permuting the bank IDs in each rectangle in

a traditional rectangularly interleaved bank ID assignment (left),

so that the pixels having the same bank ID are placed

at the center and the vertices of nearly regular hexagons packed in the frame buffer (right).

home